# Fuji Switching Power Supply Control IC

# Green mode PWM IC

# FA8A60/61/70/71

# **Application Note**

February 2013 Fuji Electric Co., Ltd.

Fuji Electric Co., Ltd.

1

FA8A60/61/70/71

#### Caution

1. The contents of this note (Product Specification, Characteristics, Data, Materials, and Structure etc.) were prepared in February 2013.

The contents will subject to change without notice due to product specification change or some other reasons. In case of using the products stated in this document, the latest product specification shall be provided and the data shall be checked.

- 2. The application examples in this note show the typical examples of using Fuji products and this note shall neither assure to enforce the industrial property including some other rights nor grant the license.

- Fuji Electric Co.,Ltd. is always enhancing the product quality and reliability. However, semiconductor products may get out of order in a certain probability. Measures for ensuring safety, such as redundant design, spreading fire protection design, malfunction protection design shall be taken, so that Fuji Electric semiconductor product may not cause physical injury, property damage by fire and social damage as a result.

- 4. Products described in this note are manufactured and intended to be used in the following electronic devices and electric devices in which ordinary reliability is required:

- Computer OA equipment Communication equipment (Pin) Measuring equipment

- Machine tool Audio Visual equipment Home appliance Personal equipment

- Industrial robot etc.

- 5. Customers who are going to use our products in the following high reliable equipments shall contact us surely and obtain our consent in advance. In case when our products are used in the following equipment, suitable measures for keeping safety such as a back-up-system for malfunction of the equipment shall be taken even if Fuji Electric semiconductor products break down:

- Transportation equipment (in-vehicle, in-ship etc.) Communication equipment for trunk line

- Traffic signal equipment Gas leak detector and gas shutoff equipment

- Disaster prevention/Security equipment Various equipment for the safety.

- 6. Products described in this note shall not be used in the following equipments that require extremely high reliability:

- Space equipment Aircraft equipment Atomic energy control equipment

- Undersea communication equipment Medical equipment.

- 7. When reprinting or copying all or a part of this note, our company's acceptance in writing shall be obtained.

- 8. If obscure parts are found in the contents of this note, contact Fuji Electric Co.,Ltd. or a sales agent before using our products. Fuji Electric Co.,Ltd. and its sales agents shall not be liable for any damage that is caused by a customer who does not follow the instructions in this cautionary statement.

# Contents

| 1. | Overview                            | ••••• | 4             |

|----|-------------------------------------|-------|---------------|

| 2. | Features                            | ••••• | 4             |

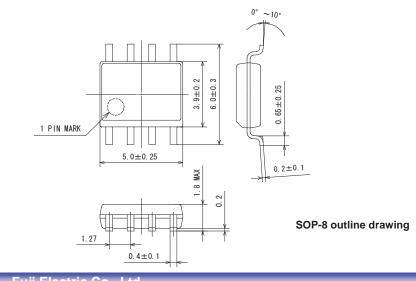

| 3. | Outline drawing                     | ••••• | 4             |

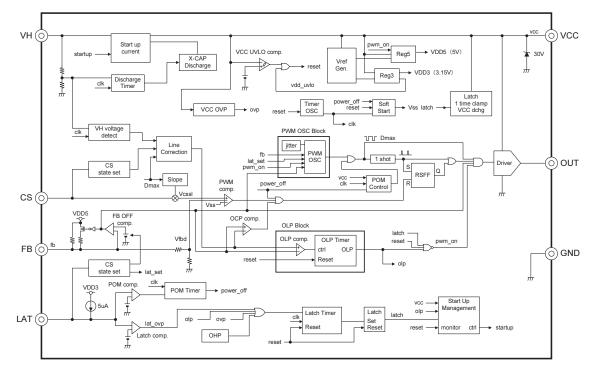

| 4. | Block diagram                       | ••••• | 5             |

| 5. | Functional description of pins      | ••••• | 5             |

| 6. | Rating & Characteristics            | ••••• | 6 <b>~</b> 16 |

| 7. | Characteristics                     | ••••• | 17~19         |

| 8. | Description of the function         |       | 20~28         |

| 9. | How to use pin and advice designing | ••••• | 29~39         |

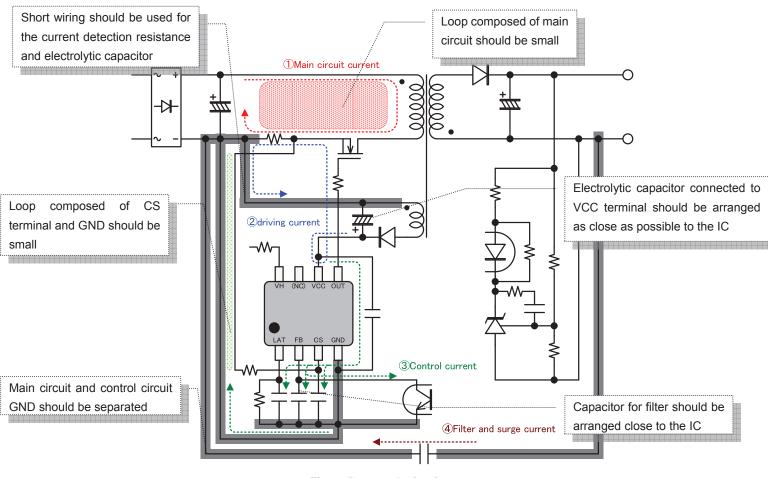

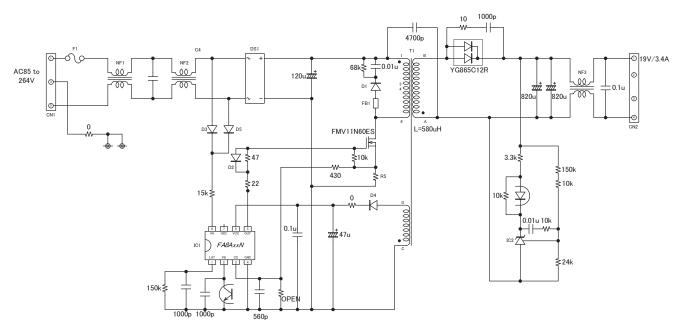

| 10 | Precautions for pattern design      | ••••• | 40            |

| 11 | Application circuit example         |       | 41            |

#### Caution)

•The contents of this note will subject to change without notice due to improvement.

• The application examples or the components constants in this note are shown to help your design, and variation of components and service conditions are not taken into account. In using these components, a design with due consideration for these conditions shall be conducted.

# 1. Overview

FA8A27N is a current mode type switching power supply control IC possible to drive a power MOSFET directly. Despite of a small package with 8 pins, it has a lot of functions and it is best suited for power saving at the light load and decreasing external parts. Moreover it enables to realize a reduced space and a high cost-performance power supply.

## 2. Features

## Relization of low standby power

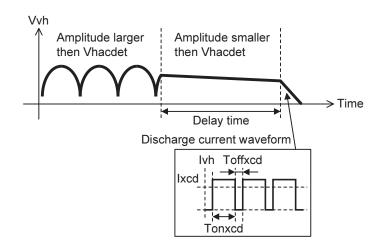

- Built-in discharge function for AC input filter capacitor (XCAP). (Reduce loss of the discharge resistor)

- Integrated frequency decrease function improves efficiency in the middle-load region. (Frequency decrease start point is adjustable based on the settings of mounted parts.)

- Intermittent operation (burst operation) system adopted for light load operation achieves low standby power. (Burst operation start point is adjustable based on the settings of mounted parts.)

- Switching is allowed between normal operation mode and power-off mode. In power-off mode, lower standby power is ensured.

- Built-in 500V high voltage startup circuit.

#### ■ Various Protection are built in.

- Overload protection (Auto recovery, Latch)

- Integrated function of correcting overload detection level depending on AC input voltage (Correction amount is adjustable based on the settings of externally mounted parts.)

- Integrated latch-off function based on external signals, overvoltage protection function, low-voltage prevention function, and overheat protection function

- nternal Soft-Start

- The lowest frequency is set to 25 kHz to prevent operation at audible frequency under light load.

- Switching frequency jitter function realize low EMI.

- Internal DSS (Dynamic Self Supply)

- Drive circuit for MOSFET: -0.5A(sink)/0.5A(source)

#### Function list by types

| Туре    | Discharge function<br>for X-Capacitor | Overload protection | External latch, over-voltage<br>protection, Over heat<br>protection | Brown out<br>protection |

|---------|---------------------------------------|---------------------|---------------------------------------------------------------------|-------------------------|

| FA8A60N | No                                    | Automatic recovery  | Latch                                                               | No                      |

| FA8A61N | INO                                   | Latch               | Laton                                                               | NO                      |

| FA8A70N | Yes                                   | Automatic recovery  | Latch                                                               | No                      |

| FA8A71N | 165                                   | Latch               |                                                                     | UNI                     |

\* Models scheduled to be serialized at present are not equipped with the brown out protection.

# 3. Outline drawing

🔁 🛛 Fuji Electric Co., Ltd

# 4. Block diagram

# FA8A61N(example)

# 5. Functional description of pins

| Pin No. | Pin name | Pin Function                                                                                                                | Note |

|---------|----------|-----------------------------------------------------------------------------------------------------------------------------|------|

| 1       | LAT      | External latch signal input<br>Switching Frequency Reduction (S.F.R.) setup<br>Switching stop FB threshold voltage setup    | *1   |

| 2       | FB       | Feedback control signal input                                                                                               | *1   |

| 3       | CS       | Current sense input, Over Load Protection (OLP), Over<br>Current Protection (OCP)<br>OLP Line Compensation (OLP L.C.) setup | *1   |

| 4       | GND      | Ground                                                                                                                      | —    |

| 5       | OUT      | Output                                                                                                                      | —    |

| 6       | VCC      | Power supply, Under Voltage Locking Out (UVLO),<br>Over Voltage Protection (OVP) detection                                  | *1   |

| 7       | (NC)     | No connection                                                                                                               | —    |

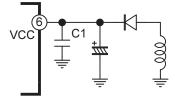

| 8       | VH       | High voltage input<br>AC Input filter capacitance (XCAP) discharge                                                          | *2   |

\*1 Connect capacitor between terminal 1pin and GND.

\*2 Connect diodes and resistor between VH and the AC lines.

Fuji Electric Co., Ltd.

# 6. Rating & characteristics

# (1) Absolute maximum ratings

Stress exceeding absolute maximum ratings may malfunction or damage the device.

"-" shows source and "+" shows sink in current descriptions.

|                        | Item                   | Symbol  | Value           | Unit |

|------------------------|------------------------|---------|-----------------|------|

| LAT pin voltage        |                        | Vlat    | -0.3 to 3.3     | V    |

| LAT pin current        |                        | llat    | -100 to 100     | μA   |

| FB pin voltage         |                        | Vfb     | -0.3 to 5.3     | V    |

| FB pin current         |                        | lfb     | -200 to 100     | μA   |

| CS pin voltage         |                        | Vcs     | -0.3 to 3.3     | V    |

| CS pin current         |                        | lcs     | -100 to 100     | μA   |

| OUT pin voltage        |                        | Vout    | -0.3 to VCC+0.3 | V    |

| OUT pin current        |                        | lout    | -500 to 500     | mA   |

| OUT pin peak current   | *3,4                   | lout_pk | -1000 to 1000   | mA   |

| VCC pin voltage        |                        | Vcc     | -0.3 to 28.0    | V    |

| VCC pin current *1     | At pulse voltage input | lvcc1   | -10 to 20       | mA   |

|                        | At minus voltage input | lvcc2   | -0.1 to 0       | mA   |

| VH pin voltage         |                        | Vvh     | -0.3 to 500     | V    |

| VH pin current *3      |                        | lvh     | -0.1 to 10      | mA   |

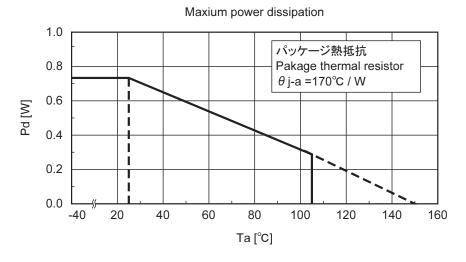

| Power dissipation (Ta  | =25°C)                 | Pd      | 735             | mW   |

| Operating junction tem | perature               | Tj      | -30 to 150      | °C   |

| Storage temperature    |                        | Tstg    | -40 to 150      | °C   |

Notes)

\*3 Please consider power supply voltage and load current well and use this IC within maximum temperature in o peration. The IC may cross maximum power dissipation at normal operating condition by power supply voltage or

load current within peak current absolute maximum rating value. \*4 The period that exceeds 500mA must be 100ns or less.

<sup>4</sup> The period that exceeds 500mA must be 100hs or les

\*Maximum dissipation curve

Fuji Electric Co., Ltd.

# (2) Recommended operating conditions

|                                | Item                               | Symbol | MIN  | TYP  | MAX  | Unit |

|--------------------------------|------------------------------------|--------|------|------|------|------|

| Supply voltag                  | ge                                 | Vcc    | 10   | 18   | 24   | V    |

| VH input                       | in start-up current supplied       | Vvh    | 50   | _    | 400  | V    |

| voltage                        | in start-up current stopped        | Vvh    | 100  | _    | 400  | V    |

| Resistor con                   | nected to VH pin *5                | Rvh    | 5.6  | —    | 50   | kohm |

| Capacitor co                   | nnected to VH pin *6               | Cvh    | 0    | —    | 100  | pF   |

| Capacitor co<br>S.F.R. : "High | nnected to LAT pin *7, 9<br>ı"     | Clat   | 176  | 220  | 264  | pF   |

| Capacitor co<br>S.F.R. : "Mide | nnected to LAT pin *7, 9<br>dle"   | Clat   | 800  | 1000 | 1200 | pF   |

| Capacitor co<br>S.F.R. : "Low  | nnected to LAT pin *7, 9<br>"      | Clat   | 2640 | 3300 | 3960 | pF   |

| Resistor con                   | nected to LAT pin *9               | Rlat   | 150  | —    | 300  | kohm |

| Resistor con<br>OLP L.C. : "N  | nected to CS pin *8, 9<br>/liddle" | Rcs    | 0.3  | _    | 0.5  | kohm |

| Resistor con<br>OLP L.C. : "V  | nected to CS pin *8, 9<br>Veak"    | Rcs    | 1.4  | _    | 2.1  | kohm |

| Resistor con<br>OLP L.C. : "S  | nected to CS pin *8, 9<br>Strong"  | Rcs    | 3.9  | _    | 5.2  | kohm |

| Capacitor co                   | nnected to VCC pin                 | Cvcc   | 22   | 33   | 56   | μF   |

| Ambiance te                    | mperature in operation             | Та     | -30  | —    | 105  | °C   |

Notes)

\*5 More than AC85V.

\*6 Verify no malfunction of XCAP discharge function occurs in case of the capacitor connection.

\*7 See terms concerning to switching frequency reduction characteristics in "3-4. PWM Oscillator" in "3. DC electrical characteristics".

\*8 See terms concerning to OLP line compensation characteristics in "3-6. Over load protection and current sense" in "3. DC electrical characteristics".

\*9 Connect to GND pin by the shortest distance as much as possible. In selection of these external components, make is sure that their values including temperature characteristics are satisfied with the recommended ranges.

# (3) DC electrical characteristics

The characteristics in this section are those in conditions as follows unless otherwise specified. The voltages described in the conditions are DC input values (not AC input values).

Tj = 25°C, VCC = 18V, VVH = 120V, Vlat = 1.0V, VFB = 2.5V, VCS = 0V Initial Setup: Switching Frequency Reduction: "Low", OLP Line Compensation: "Middle"

Notes)

(1)The item which indicated "\*1" are not 100% tested in production but guaranteed by design. (2)No guaranteed value exists for the column of "-".

(3)"-" shows source current and "+" shows sink current in current output characteristics.

3-1. Initial setup function (CS, LAT pins)

| Item                                              | Symbol   | Condition                      | Min. | Тур. | Max. | Unit |

|---------------------------------------------------|----------|--------------------------------|------|------|------|------|

| Initial setup time                                | Tiniset  |                                | 84   | 95   | 106  | μs   |

| LAT source current<br>for capactance detection    | llatset  | Vlat = 0V,<br>In initial setup | -55  | -50  | -45  | μA   |

| LAT threshold voltage<br>for capactance detection | Vlatset  | In initial setup               | 1.5  | 1.6  | 1.7  | V    |

| LAT threshold time (1) for capactance detection   | Tlatset1 | In initial setup               | 16   | 19   | 22   | μs   |

| LAT threshold time (2) for capactance detection   | Tlatset2 | In initial setup               | 62   | 69   | 77   | μs   |

| CS source current<br>for resistance detection     | lcsset   | In initial setup               | 85   | 100  | 115  | μA   |

| CS threshold voltage (1) for resistance detection | Vcsset1  | In initial setup               | 70   | 95   | 120  | mV   |

| CS threshold voltage (2) for resistance detection | Vcsset2  | In initial setup               | 260  | 295  | 330  | mV   |

| LAT sink current in UVLO                          | llatsiuv | Vvcc = 6V,<br>Vlat = 1.5V      | 0.6  | 1.3  | 2    | mA   |

| LAT pin<br>test mode set voltage                  | Vlattest |                                | 0.7  | 1.1  | 1.5  | V    |

| CS sink current in UVLO                           | Icssiuv  | Vvcc = 6V,<br>Vcs = 1.5V       | 0.4  | 1.0  | 1.6  | mA   |

3-2. External latch-off function (LAT pin)

| Item                                   | Symbol  | Condition       | Min. | Тур. | Max. | Unit |

|----------------------------------------|---------|-----------------|------|------|------|------|

| LAT output current                     | llatsrc |                 | -5.5 | -5   | -4.5 | μA   |

| LAT threshold voltage for<br>latch-off | VthlatH | Vlat increasing | 1.6  | 1.8  | 2.0  | V    |

| Latch-off delay time                   | Tdlylat | Vlat > VthlatH  | 57   | 72   | 88   | μs   |

Notes)

Switching is stopped in latch mode when LAT pin voltage Vlat is kept higher than Vthlath for Tdlylat.

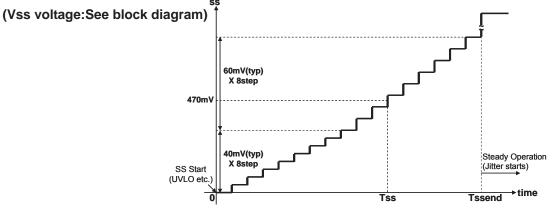

# 3-3. Soft-start function (OUT pin)

| Item                                     | Symbol | Condition                                              | Min. | Тур. | Max. | Unit |

|------------------------------------------|--------|--------------------------------------------------------|------|------|------|------|

| Soft-start time *10                      | Tss    | Vss = 470mV<br>(internal voltage to PWM<br>comparator) | 8.5  | 11   | 13.5 | ms   |

| Steady-state operation start time *10,11 | Tssend |                                                        | 14   | 17   | 20   | ms   |

Notes)

\*10 During start-up after UVLO and Power off mode (see "10-12. Power off mode section") .

\*11 Switching frequency jitter starts. Minmum ON pulse width : Tmin2 →Tmin1 (see "3-5. Pulse width modulation section")

#### 3-4. PWM oscilator (FB, OUT pin)

| Item                                  | Symbol | Condition                                     | Min. | Тур. | Max. | Unit |

|---------------------------------------|--------|-----------------------------------------------|------|------|------|------|

| Switching frequency                   | Fsw    |                                               | 62   | 65   | 68   | kHz  |

| Supply voltage stability              | FswdV  | Vvcc = 10V to 24V                             | -2   | —    | 2    | %    |

| Temperature stability *1              | FswdT  | Tj = -30°C to 105°C                           | -5   | —    | 5    | %    |

| Frequency modulation ratio *1         | Rfm    | Vfb > Vfbh_h<br>⊿Fsw / Fsw                    | ±5   | ±7   | ±9   | %    |

| Frequency modulation period *1        | Tfm    | Vfb > Vfbh_h                                  | 1    | 2    | 3    | ms   |

| Frequency reduction start FB voltage  | Vfbh_h | S. F. R. : "High" *12<br>Freq. = Fsw×0.9      | 1.67 | 1.97 | 2.27 | V    |

| Frequency reduction end<br>FB voltage | Vfbl_h | S. F. R. : "High" *12<br>Freq. = Fswmin×1.1   | 1.55 | 1.85 | 2.15 | V    |

| Frequency reduction range width       | Vfbd_h | Vfbh_h – Vfbl_h                               | 0.06 | 0.14 | 0.22 | V    |

| Frequency reduction start FB voltage  | Vfbh_m | S. F. R. : "Middle" *12<br>Freq. = Fsw×0.9    | 1.46 | 1.76 | 2.06 | V    |

| Frequency reduction end<br>FB voltage | Vfbl_m | S. F. R. : "Middle" *12<br>Freq. = Fswmin×1.1 | 1.35 | 1.65 | 1.95 | V    |

| Frequency reduction<br>range width    | Vfbd_m | Vfbh_m – Vfbl_m                               | 0.05 | 0.12 | 0.19 | V    |

| Frequency reduction start FB voltage  | Vfbh_l | S. F. R. : "Low" *12<br>Freq. = Fsw×0.9       | 1.05 | 1.35 | 1.65 | V    |

| Frequency reduction end FB voltage    | Vfbl_l | S. F. R. : "Low" *12<br>Freq. = Fswmin×1.1    | 0.98 | 1.28 | 1.58 | V    |

| Frequency reduction range width       | Vfbd_I | Vfbh_l – Vfbl_l                               | 0.04 | 0.10 | 0.16 | V    |

| Minimum switching<br>frequency        | Fswmin | Vfb = 0.7V                                    | 22.5 | 25   | 27.5 | kHz  |

Notes)

\*12 Conncerning to setup condition, see "3-1. Initial setup function" and "9. Recommended operation conditions".

Fuji Electric Co., Ltd.

## FA8A60/61/70/71

| Item                                      | Symbol | Condition        | Min. | Тур. | Max. | Unit  |

|-------------------------------------------|--------|------------------|------|------|------|-------|

| Maximum duty cycle                        | Dmax   |                  | 73   | 83   | 93   | %     |

| Minimum duty cycle                        | Dmin   | Vfb = 0V         | _    | _    | 0    | %     |

| FB threshold voltage for                  | Vthfb  | Vlat = 0.75V *13 | 0.42 | 0.47 | 0.52 | V     |

| stop switching                            | Vinio  | Vlat = 1.5V *13  | 0.84 | 0.94 | 1.04 | V     |

| FB output current                         | lfbsrc | Vfb = 0V         | -95  | -75  | -55  | μA    |

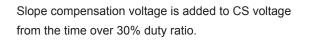

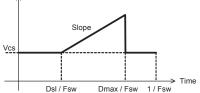

| Slope compensation                        | Slope  |                  | 14   | 21   | 28   | mV/µs |

| Duty ratio at starting slope compensation | Dsl    |                  | 20   | 30   | 40   | %     |

| Minimum ON pulse width                    | Tmin1  | In steady state  | 400  | 560  | 720  | ns    |

|                                           | Tmin2  | In soft start    | 180  | 280  | 380  | ns    |

\*13 Adjustable with Rlat (Vlat = Rlat  $\times$  -llatsrc) .

Vcssl (internal voltage, coompared to Vfbd)

Slope compensation waveform

# 3-6. Over load protection and current sense (FB, CS pin)

| Iter                            | n                        | Symbol                                                                                   | Condition                                                                    | Min. | Тур. | Max. | Unit |

|---------------------------------|--------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|------|------|------|

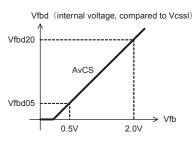

|                                 |                          | Vfbd05                                                                                   | Vlat = 0.7V                                                                  | 10   | 50   | 90   | mV   |

| FB divided voltag               | e                        |                                                                                          | Vfb = 0.5V                                                                   |      |      |      |      |

|                                 |                          | Vfbd20                                                                                   | Vlat = 0.7V<br>Vfb = 2.0V                                                    | 300  | 360  | 420  | mV   |

| Voltage gain                    |                          | AvCS                                                                                     | 1.5/(Vfbd20-Vfbd05)                                                          | 4.3  | 4.8  | 5.3  | V/V  |

|                                 |                          | Vthcs1a                                                                                  | $Vvhp \le Vvhd3$                                                             | 0.46 | 0.50 | 0.54 | V    |

|                                 |                          | Vthcs1b                                                                                  | Vvhd3 <vvhp<u>&lt;Vvhd4</vvhp<u>                                             | 0.44 | 0.48 | 0.52 | V    |

|                                 | Vthcs1c                  | Vvhd4 <vvhp≤vvhd5< td=""><td>0.42</td><td>0.46</td><td>0.50</td><td>V</td></vvhp≤vvhd5<> | 0.42                                                                         | 0.46 | 0.50 | V    |      |

|                                 |                          | Vthcs1d                                                                                  | Vvhd5 <vvhp<u>&lt;Vvhd6</vvhp<u>                                             | 0.40 | 0.44 | 0.48 | V    |

|                                 | OLP.L.C.                 | Vthcs1e                                                                                  | Vvhd6 < Vvhp                                                                 | 0.38 | 0.42 | 0.46 | V    |

|                                 | "Middle" *14             | Vthcs1ab                                                                                 | Vthcs1a-Vthcs1b                                                              | 0.01 | 0.02 | 0.03 | V    |

|                                 |                          | Vthcs1bc                                                                                 | Vthcs1b-Vthcs1c                                                              | 0.01 | 0.02 | 0.03 | V    |

|                                 |                          | Vthcs1cd                                                                                 | Vthcs1c-Vthcs1d                                                              | 0.01 | 0.02 | 0.03 | V    |

|                                 |                          | Vthcs1de                                                                                 | Vthcs1d-Vthcs1e                                                              | 0.01 | 0.02 | 0.03 | V    |

|                                 |                          | Vthcs2a                                                                                  | Vvhp ≤ Vvhd3                                                                 | 0.46 | 0.50 | 0.54 | V    |

|                                 |                          | Vthcs2b                                                                                  | Vvhd3 <vvhp<u>&lt;Vvhd4</vvhp<u>                                             | 0.46 | 0.50 | 0.54 | V    |

| CS threshold                    |                          | Vthcs2c                                                                                  | Vvhd4 <vvhp<u>&lt;Vvhd5</vvhp<u>                                             | 0.44 | 0.48 | 0.52 | V    |

| voltage for over                | OLP.L.C.<br>"Weak" *14   | Vthcs2d                                                                                  | Vvhd5 <vvhp<u>&lt;Vvhd6</vvhp<u>                                             | 0.42 | 0.46 | 0.50 | V    |

| load protection                 |                          | Vthcs2e                                                                                  | Vvhd6 <vvhp< td=""><td>0.40</td><td>0.44</td><td>0.48</td><td>V</td></vvhp<> | 0.40 | 0.44 | 0.48 | V    |

|                                 |                          | Vthcs2bc                                                                                 | Vthcs2b-Vthcs2c                                                              | 0.01 | 0.02 | 0.03 | V    |

|                                 |                          | Vthcs2cd                                                                                 | Vthcs2c-Vthcs2d                                                              | 0.01 | 0.02 | 0.03 | V    |

|                                 |                          | Vthcs2de                                                                                 | Vthcs2d-Vthcs2e                                                              | 0.01 | 0.02 | 0.03 | V    |

|                                 |                          | Vthcs3a                                                                                  | Vvhp <u>≤</u> Vvhd3                                                          | 0.46 | 0.50 | 0.54 | V    |

|                                 |                          | Vthcs3b                                                                                  | Vvhd3 <vvhp<u>&lt;Vvhd4</vvhp<u>                                             | 0.44 | 0.48 | 0.52 | V    |

|                                 |                          | Vthcs3c                                                                                  | Vvhd4 <vvhp<u>&lt;Vvhd5</vvhp<u>                                             | 0.40 | 0.44 | 0.48 | V    |

|                                 |                          | Vthcs3d                                                                                  | Vvhd5 <vvhp<u>&lt;Vvhd6</vvhp<u>                                             | 0.38 | 0.42 | 0.46 | V    |

|                                 | OLP.L.C.<br>"Strong" *14 | Vthcs3e                                                                                  | Vvhd6 < Vvhp                                                                 | 0.36 | 0.40 | 0.44 | V    |

|                                 | Strong 14                | Vthcs3ab                                                                                 | Vthcs3a-Vthcs3b                                                              | 0.01 | 0.02 | 0.03 | V    |

|                                 |                          | Vthcs3bc                                                                                 | Vthcs3b-Vthcs3c                                                              | 0.02 | 0.04 | 0.06 | V    |

|                                 |                          | Vthcs3cd                                                                                 | Vthcs3c-Vthcs3d                                                              | 0.01 | 0.02 | 0.03 | V    |

|                                 |                          | Vthcs3de                                                                                 | Vthcs3d-Vthcs3e                                                              | 0.01 | 0.02 | 0.03 | V    |

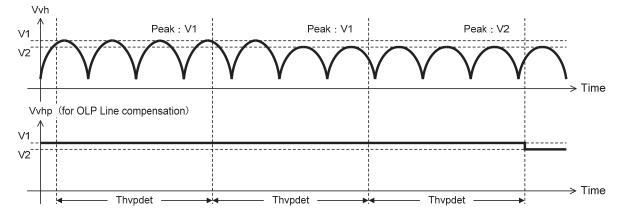

| VH peak voltage detection time  |                          | Tvhpdet                                                                                  |                                                                              | 56   | 64   | 72   | ms   |

| Over current protection delay t | ime                      | Tdlyocp                                                                                  | Vcs = 0V to 1.5V<br>(pulse signal)                                           | 20   | 50   | 150  | ns   |

| Over load protect delay time    |                          | Tdlyolp                                                                                  | Vcs > Vthcsxx                                                                | 160  | 200  | 240  | ms   |

\*14 Conncerning to setup condition, see "3-1. Initial setup function" and

"2. Recommended operation conditions".Conncerning to VH pin voltage condition, see OLP line compensation boundary voltage in "3-1. Initial setup function".

Relation of FB voltage to FB divided voltage is shown in the following figure.

Relation of FB voltage Vfb to FB divided voltage Vfbd

VH peak voltage Vhp for OLP line compensation is detected and reloaded in every Tvhpdet.

VH peak voltage detection method

When CS voltage Vcs exceeds to OLP threshold voltage Vthcs, OUT is turned off after Tdlyocp, and over load flag is set to High. This flag is sampled with 0.5ms interval, and value of UP/DOWN counter for OLP increases or decrease based on whether it is High or Low respectively. If the value of UP/DOWN counter reaches 384, IC switches latch-off mode.

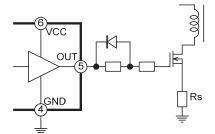

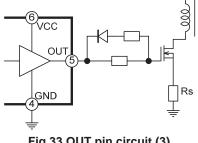

#### 3-7. Drive output (OUT pin)

| Item                   | Symbol   | Condition                 | Min. | Тур. | Max. | Unit |

|------------------------|----------|---------------------------|------|------|------|------|

| Output low voltage     | Voutl    | Vfb = 0V,<br>lout = 100mA | 0.5  | 1.5  | 2.5  | V    |

| Output high voltage *1 | Vouth    | lout = -50mA              | 14.5 | 16.0 | 17.5 | V    |

| Output voltage at UVLO | Voutuvlo | Vvcc = 6V,<br>Iout = 5mA  | 50   | 100  | 300  | mV   |

| Rise time *1           | Trise    | Vvcc = 24V,<br>Cout = 1nF | 40   | 80   | 120  | ns   |

| Fall time *1           | Tfall    | Vvcc = 24V,<br>Cout = 1nF | 20   | 40   | 70   | ns   |

#### 3-8. VCC section (VCC pin)

| Item                                      | Symbol    | Condition             | Min. | Тур. | Max. | Unit |

|-------------------------------------------|-----------|-----------------------|------|------|------|------|

| UVLO release voltage                      | Vvccon    | Vvcc increasing       | 11.5 | 12.5 | 13.5 | V    |

| UVLO voltage                              | Vvccoff   | Vvcc decreasing       | 6.0  | 6.5  | 7.0  | V    |

| UVLO hysteresis                           | Vvcchys   | Vvccon-Vvccoff        | 5.0  | 6.0  | 7.0  | V    |

| UVLO release delay time *1                | Tdlyvccon | Time to initial setup | 50   | 70   | 90   | μs   |

| Over voltage protection threshold voltage | Vthovp    | Vvcc increasing       | 24.5 | 25.5 | 26.5 | V    |

| Over voltage proteciton delay time *1     | Tdlyovp   | Vvcc > Vthovp         | 57   | 72   | 88   | μs   |

| VCC voltage for DSS                       | Vvccdssh  | Vvcc increasing       | 8.0  | 8.5  | 9.0  | V    |

| VCC Vollage for DSS                       | Vvccdssl  | Vvcc decreasing       | 7.5  | 8.0  | 8.5  | V    |

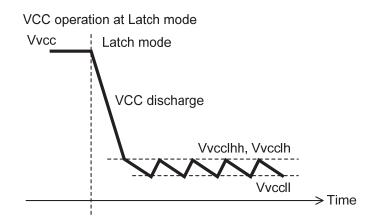

|                                           | Vvcclhh   | Vvcc discharge end    | 8.0  | 8.5  | 9.0  | V    |

| VCC voltage at latch-off                  | Vvcclh    | Vvcc upper level      | 8.0  | 8.5  | 9.0  | V    |

|                                           | Vvccll    | Vvcc lower level      | 7.5  | 8.0  | 8.5  | V    |

🗧 Fuji Electric Co., Ltd.

#### Note)

DSS function : Even in case that VCC pin voltage decreases in normal operation, the start-up circuit operates for Vvcc to keep between Vvccdssh and Vvccdssl.

Switching is stopped in latch mode when VCC pin voltage Vvcc is kept higher than Vthovp for Tdlyovp.

On entering latch mode, capacitance connected to VCC pin is discharged by supply current in latch-off (Ivcclatcl:

see "3-9. Power supply current") . After that, the start-up circuit operates for Vvcc to keep between Vvccll and

$\ensuremath{\mathsf{Vvcclh}}\xspace$  , which prevents from operating UVLO and maintains latch mode.

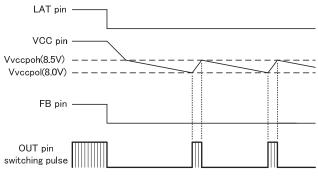

An operating waveform in latch-off mode

3-9. Power supply current (VCC pin)

| Item                                     | Symbol    | Condition                            | Min. | Тур. | Max. | Unit |

|------------------------------------------|-----------|--------------------------------------|------|------|------|------|

| Supply current in operating              | lvccop1   | Ivccop1 OUT no load                  |      | 0.6  | 1.0  | mA   |

| Supply current in operating              | lvccop2   | Vfb = 0V                             | 0.2  | 0.3  | 0.6  | mA   |

| Supply surront in latch off              | Ivcclatcl | Vvh=0V, Vvcc=15V                     | 3.5  | 6    | 10   | mA   |

| Supply current in latch-off              | lvcclat   | VVh=0V, Vvcc=8V                      | 0.2  | 0.3  | 0.45 | mA   |

| Supply current<br>in power off mode      | lvccpom   | Vlat = 0V,<br>Vvcc = 9V,<br>Vvh = 0V | 0.05 | 0.15 | 0.3  | mA   |

| Supply current just before UVLO released | lvccuv    | Vvh = 0V,<br>Vvcc= Vcc-0.1V          | 0.05 | 0.15 | 0.3  | mA   |

# 3-10. High-voltage input section (VCC, VH pin)

| Item                                       | Symbol   | Condition                               | Min. | Тур. | Max. | Unit |

|--------------------------------------------|----------|-----------------------------------------|------|------|------|------|

|                                            | lvhrun   | Vvh = 450Vdc                            | 3    | 5    | 20   | μA   |

|                                            |          | Vvh = 50Vdc,<br>Vvcc = 0V               | 0.4  | 0.8  | 1.6  | mA   |

| VH input current                           | lvhstb   | Vvh = 50Vdc,<br>Vvcc = 6V to 11V        |      | 3.0  | 4.0  | mA   |

|                                            |          | Vvh = 50Vdc,<br>Vvcc = Vvccon - 0.1V    | 1.3  | 3.0  | 4.0  | mA   |

|                                            |          | Vvh = 50Vdc,<br>Vvcc = 0V               | -1.6 | -0.8 | -0.4 | mA   |

| Charge current for VCC                     | Ipre     | Vvh = 50Vdc,<br>Vvcc = 6V to 11V        | -3.7 | -2.7 | -1.7 | mA   |

|                                            |          | Vvh = 50Vdc,<br>Vvcc=Vvccon-0.1V        | -3.7 | -2.7 | -1.0 | mA   |

| Start-up circuit<br>consumption current    | lvhint   | lvhstb-lpre-lvcc,<br>Vvcc = Vvccon-0.1V | 0.01 | 0.05 | 0.10 | mA   |

|                                            | Vvhd3h   | Vvh increasing                          | 126  | 138  | 150  | Vdc  |

| OLP L.C.<br>boundary voltage (3)           | Vvhd3l   | Vvh decreasing                          | 114  | 125  | 136  | Vdc  |

| Soundary Voltago (0)                       | Vvhd3d   | Vvhd3h-Vvhd3l                           | 7.5  | 12.5 | 17.5 | Vdc  |

|                                            | Vvhd4h   | Vvh increasing                          | 161  | 175  | 189  | Vdc  |

| OLP L.C.<br>boundary voltage(4)            | Vvhd4l   | Vvh decreasing                          | 150  | 163  | 176  | Vdc  |

|                                            | Vvhd4d   | Vvhd4h-Vvhd4l                           | 7.5  | 12.5 | 17.5 | Vdc  |

|                                            | Vvhd5h   | Vvh increasing                          | 209  | 225  | 241  | Vdc  |

| OLP L.C.                                   | Vvhd5l   | Vvh decreasing                          | 197  | 213  | 229  | Vdc  |

| boundary voltage (5)                       | Vvhd5d   | Vvhd5h-Vvhd5l                           | 7.5  | 12.5 | 17.5 | Vdc  |

|                                            | Vvhd6h   | Vvh increasing                          | 257  | 275  | 393  | Vdc  |

| OLP L.C.                                   | Vvhd6l   | Vvh decreasing                          | 245  | 263  | 281  | Vdc  |

| boundary voltage (6)                       | Vvhd6d   | Vvhd6h-Vvhd6l                           | 7.5  | 12.5 | 17.5 | Vdc  |

| 3-11. XCAP discharge circuit (\            | /H pin)  | I                                       | I    | 1    | I    | II   |

| Item                                       | Symbol   | Condition                               | Min. | Тур. | Max. | Unit |

| Average discharge<br>current for XCAP *1   | Ixcd     | In XCAP discharge                       | 1    | 2    | 4    | mA   |

| ON-time for XCAP<br>discharge current      | Tonxcd   | In XCAP discharge                       | 1.2  | 1.5  | 1.8  | ms   |

| OFF-time for XCAP<br>discharge current     | Toffxcd  | In XCAP discharge                       | 0.4  | 0.5  | 0.6  | ms   |

| VH ampulitud ensured                       | Vhacdet  | Vvh = 67 to 124V                        | 50   | _    | -    | V    |

| AC detection                               | vnacuel  | Vvh = 236 to 358V                       | 75   | _    | _    | V    |

| VH ampulitud garenteed<br>AC non detection | Vhnacdet | Vvh = 67 to 97V,<br>Vvh = 281 to 358V   | _    | _    | 5    | V    |

| Delay time for<br>AC detection             | Tacdet   |                                         | 40   | 56   | 72   | ms   |

Fuji Electric Co., Ltd.

#### Note)

XCAP discharge starts after AC input is cut off and then VH voltage variation is not detected for AC detection delay time.

An operating waveform in XCAP discharge function.

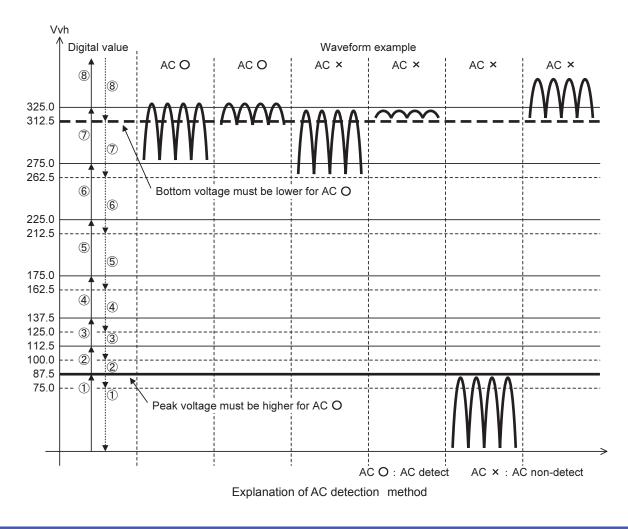

It is VH pin voltage condition for proper AC detection that its peak is more than 87.5V (design value) and its bottom is less than 312.5V (design value).

VH pin voltage is converted to one of 8 digital values with hysteresis characteristics. At least one increment of the digital value in each AC detection delay time Taccdet is required for judging AC supplies.

🔁 Fuji Electric Co., Ltd.

| Item                                             | Symbol    | Condition                           | Min. | Тур. | Max. | Unit |

|--------------------------------------------------|-----------|-------------------------------------|------|------|------|------|

|                                                  | Vthlatpol | Vthlatpol Vlat decreasing           |      | 0.55 | 0.60 | V    |

| LAT threshold voltage<br>for power off mode      | Vthlatpoh | Vlat increasing                     | 0.55 | 0.60 | 0.65 | V    |

|                                                  | Vthlatpod | Vthlatpoh-Vthlatpol                 | 0.02 | 0.05 | 0.08 | V    |

| Power off mode<br>disable time in start-up       | Tdlynopo  | oo After UVLO released              |      | 128  | 141  | ms   |

| Delau time far mede quiteb                       | Tdlypoh   | Power off mode<br>to normal mode    | 41   | 56   | 71   | μs   |

| Delay time for mode switch                       | Tdlypol   | Normal mode to power off mode       | 41   | 56   | 71   | μs   |

| VCC voltage to start switching in power off mode | Vvccpol   | Vlat < Vthlatpol<br>Vvcc decreasing | 7.5  | 8.0  | 8.5  | V    |

| VCC voltage to stop switching in power off mode  | Vvccpoh   | Vlat < Vthlatpol<br>Vvcc increasing | 8.0  | 8.5  | 9.0  | V    |

| VCC hysteresis<br>in power off mode              | Vvccpod   | Vvccpoh-Vvccpol                     | 0.2  | 0.5  | 0.8  | V    |

| ON pulse width<br>in power off mode              | Tpom      | Vlat < Vthlatpol<br>Vvcc < Vvcccpol | 1.0  | 1.4  | 1.8  | μs   |

| Switching frequency<br>in power off mode         | Fpom      | Vlat < Vthlatpol<br>Vvcc < Vvcccpol | 55   | 62.5 | 70   | kHz  |

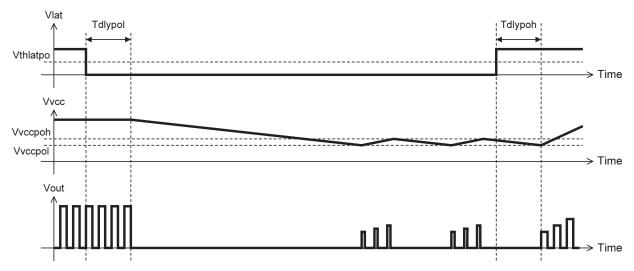

#### 3-12. Power off mode (LAT, VCC pins)

#### Note)

The controller swithes to power off mode after Vlat keeps lower than Vthlatpol for Tdlypol and returns to normal operation after Vlat keeps higher than Vthlatpoh for Tdlypoh. Inspite of this, normal operation is forced before Tdlynopo passes form release of UVLO. In power off mode, OUT pin switches with fixed frequency Fpom and pulse width Tpom for Vvcc to keep between Vvccpol and Vvccpoh by a current supply from a winding of a transformer of a power supply system. After Vlat keeps higher than Vthlatpoh for Tdlypoh, return power off mode starts.

3-13 Over heat protection

| Item                    | Symbol | Condition | Min. | Тур. | Max. | Unit |

|-------------------------|--------|-----------|------|------|------|------|

| Over heat protection    | Tohp   |           | 125  | 137  | 150  | °c   |

| operating temarature *1 | TONP   |           | 125  | 137  | 150  | C    |

When temperature exceeds Tohp and overheat protection works, OUT is turned off and IC switches latch-off mode.

🔶 Fuji Electric Co., Ltd.

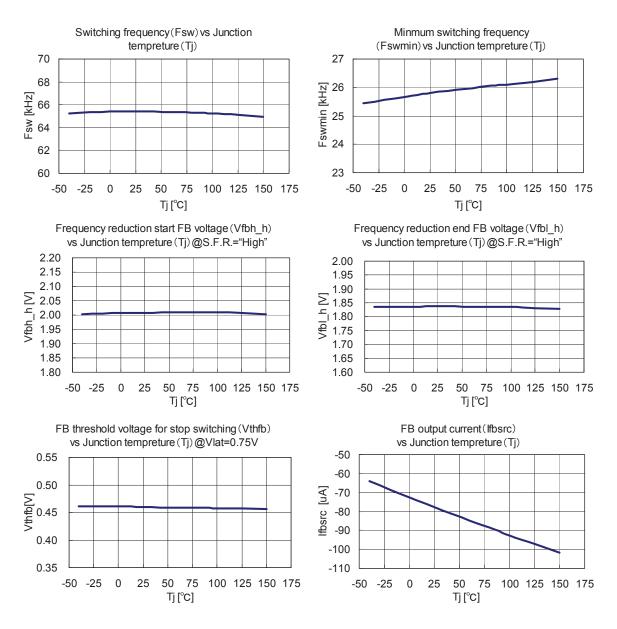

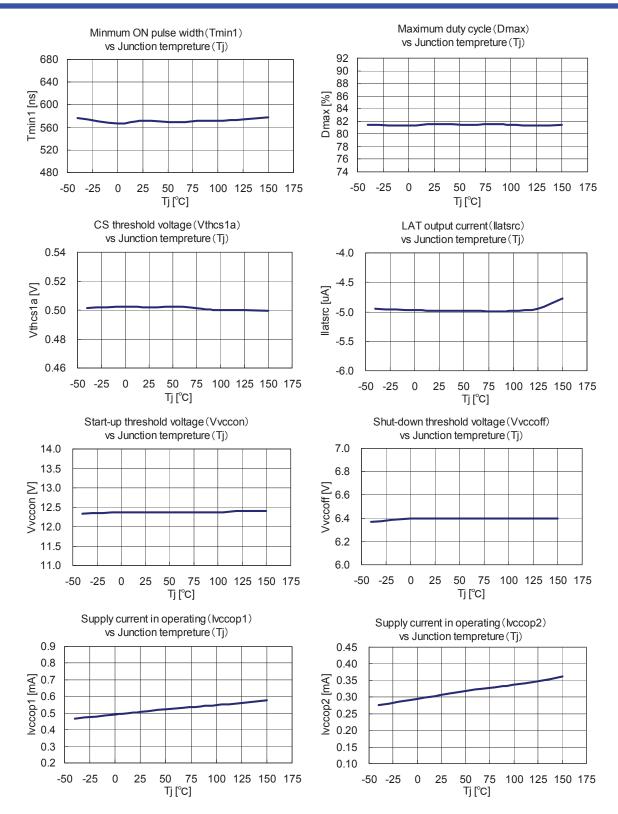

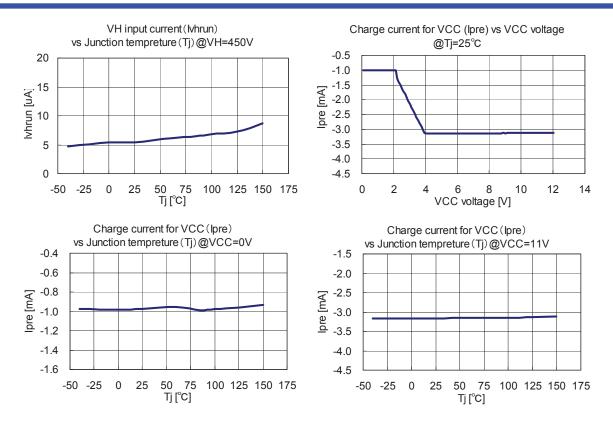

# 7. Characteristic curve

The characteristics in this section are under described conditions as follows unless otherwise specified.

Tj = 25°C, Vvcc = 18V, Vvh = 120V, Vlat = 1.0V, Vfb = 2.5V, Vcs = 0V Initial setup: S.F.R. : "Low", OLP L.C. : "Middle"

Notes)

- (1) "-" shows source current and "+" shows sink in current regulations of the current.

- (2) The data listed here show the typical characteristics of an IC, and does not guarantee the characteristic.

FA8A60/61/70/71

# **8. Description of the function** (The values in the following description are typical values unless otherwise specified.)

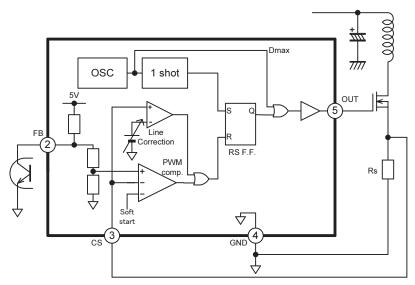

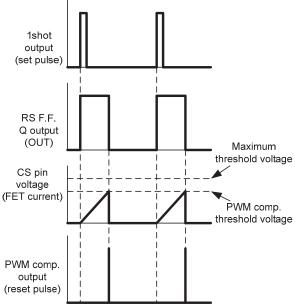

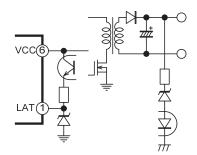

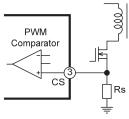

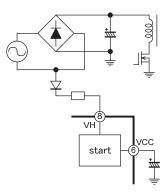

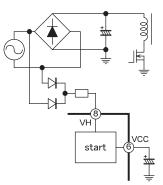

# (1) PWM control

FA8A27N performs current mode control. Fig.1 shows a circuit block for basic operations, and Fig.2 shows a timing chart. A trigger signal having the switching frequency that is output from the oscillator is input to the PWM (F.F.) through the one-shot circuit as a set signal. Then the output of the PWM as well as the OUT pin voltage reaches the High state. On the other hand, the current comparator (PWM comp.) monitors the MOSFET current, and if the threshold voltage is reached, a reset signal is output. When a reset signal is input, the output of PWM (F.F.) as well as the OUT pin voltage reaches the Low state.

Therefore, The ON pulse width of the OUT pin is thus controlled with the threshold voltage of the PWM comparator (PWM comp.).The output is controlled by changing the threshold voltage of this PWM comp. with feedback signals.

As shown in Fig.1,FB pin voltage and soft-start level input PWM comparator. These signal enabled the lower voltage, as PWM threshold voltage.

The maximum MOSFET current is limited by the voltage of line correction and current detection resistor Rs.

The oscillator outputs pulses for determining the maximum duty cycle. Using these pulses, the maximum duty cycle has been set to 83% (typ).

Fig1. Current mode basic operation circuit block

Fig2. Current mode basic operation timing chart

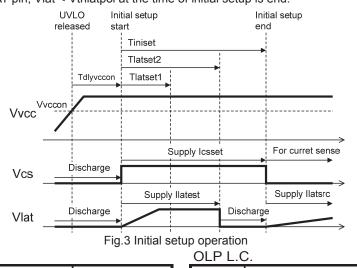

#### (2) Initial setup function

Switching frequency reduction characteristic (S.F.R.) and OLP line compensation characteristics (OLP L.C.) are decided by initial setup. Initial setup starts when UVLO release delay time (Tdlyvccon : see "3-8. VCC section") passes after UVLO is released.

S.F.R. can be chosen from three kinds of characteristics, it depends on charging time of the capacitance which connect to LAT pin. LAT pin capacitance (Clat) is charged with the current for LAT capacitance detection (Ilatset), the selection is decided by the time (LAT threshold time for capacitance detection : Tlatset1,Tlatset2) when LAT voltage (Vlat) exceeds LAT capacitance detecting voltage (Vlatset). With time for Vlat > Vlatset, "High" is chosen when shorter than Tlatset1, "Middle" is chosen at the time between Tlatset1 and Tlatse2, and "Low" is chosen when longer than Tlatset2. In addition, Clat is discharged until Tdlyvccon passes, and after Tlatset2 passes. And when Tiniset passes, initial setup is end, Ilatsrc (see "3-2. External latch-off function") is provided from LAT pin, and normal operation starts.

OLP L.C. can be chosen from three kinds of characteristics, it depends on the value of resistance (Rcs) which connect to CS pin. The selection is decided by comparison of CS pin voltage (Vcs) which is decided by flowing the current for CS resistance detection (Icsset) to Rcs and CS resistance detecting voltage (Vcsset1, Vcsset2). "Middle" is chosen when Vcs < Vcsset1, "Weak" is chosen when Vcsset1  $\leq$  Vcs  $\leq$  Vcsset2, "Strong" is chosen when Vcs > Vcsset2. In addition, Rcs is discharged until Tdlyvccon passes. And when Tiniset passes, initial setup is end, it becomes normal operation and performs a current sense.

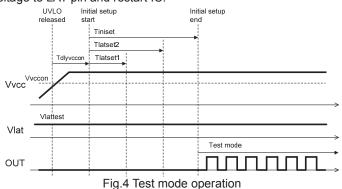

XCAP discharge and switching frequency jittering function become effective from the first time Vlat < Vthlatpol (see "3-12. Power off mode") after initial setup is end. In addition, when only recommendation resistance and capacitance are connected to LAT pin, Vlat < Vthlatpol at the time of initial setup is end.

| S. | F. | R |

|----|----|---|

|----|----|---|

| 0.1 .1 (. |                             |                          | 011 1.1    | 0.                          |                         |

|-----------|-----------------------------|--------------------------|------------|-----------------------------|-------------------------|

| Setting   | Time for Vlat > Vlatset     | Reccomended<br>Clat [pF] | Setting    | Vcs @ Tiniset               | Reccomended<br>Rcs [kΩ] |

| High      | < Tlatset1                  | 220±20%                  | Middle     | < Vcsset1                   | 0.3~0.5                 |

| Middle    | Tlateset1 ~ Tlatset2        | 1000±20%                 | Weak       | Vcsset1 ~ Vcsset2           | 1.4~2.1                 |

| Low       | > Tlatset2                  | 3300±20%                 | Strong     | > Vcsset2                   | 3.9~5.2                 |

| M/how to  | at made activated in put to | LAT min hofers LIV       | in release | d IC muna in teat meads and | a frage land            |

When test mode set voltage input to LAT pin before UVLO is released, IC runs in test mode and a frequency modulation function and a XCAP discharge function do not operate after initial setup is end. To cancel a test mode, stop inputting voltage to LAT pin and restart IC.

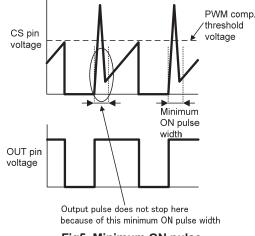

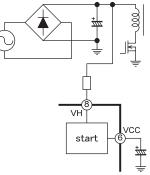

# (3) Minimum ON pulse width function

When the MOSFET is turned on, a surge current is generated due to discharge corresponding to the capacitance of the main circuit and gate drive current. If this surge current reaches the CS pin threshold voltage, normal pulses may not be generated from the OUT pin.

To avoid this phenomenon, a minimum ON width of OUT pin output is set within the one-shot circuit block of the IC.

If a trigger signal having the switching frequency is input from the oscillator, a pulse having a specific width is output as a PWM latch (F.F.) set signal.

Since the set signal has priority over the input signal of the PWM latch, the output of the PWM latch (F.F.) is not reversed while the set signal from the one-shot circuit is being input, even if a reset signal is input from the current comparator (CS comp.) (See Fig.1)

As a result, the input to the CS pin is kept invalid for the specified period of time immediately after the output pulse is generated from the OUT pin (minimum ON width), and made not to respond to the surge current at turn-on. (See Fig.5)

Fig5. Minimum ON pulse

#### (4) Frequency decrease function

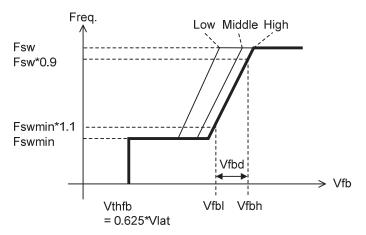

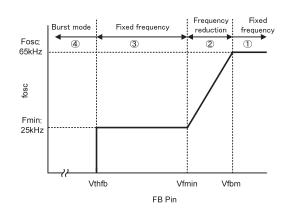

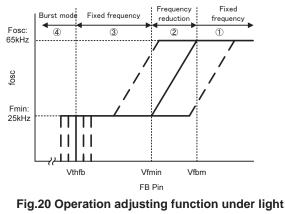

The switching frequency for normal operation mode is set to 65 kHz inside the IC. To decrease loss under light load, however, the function of decreasing switching frequency under light load is provided. Frequency under light load decreases to the lowest frequency almost linearly in proportion to the FB pin voltage. The minimum frequency is set to 25 kHz.

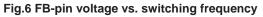

# (5) Burst operation function

To achieve low standby power, burst operation is automatically started under light load. If the FB pin voltage decreases to lower than the pulse stop FB voltage, switching is stopped. On the contrary, if the FB voltage increases to higher than the pulse stop FB voltage, switching is restarted. The FB pin voltage repeats overshoot and undershoot across the pulse stop FB voltage. Continuous pulses are output in this overshoot period, and a long stopping period is obtained in the undershoot period.

Fig.7 Burst operation at light load

#### (6) Frequency decrease start and burst operation start point adjusting function

To decrease switching loss under light load, frequency decrease function is integrated. However, if the frequency is decreased under heavy-load conditions, a problem of output ripple may arise. In addition, to achieve low standby power, burst operation function is integrated. However, if burst operation is performed under heavy-load conditions, audible noise may be generated from the transformer. With this IC, the frequency decrease start point and the burst operation start point are respectively adjusted based on the settings of the resistor and the capacitor connected between the LAT pin and the GND.

#### (7) Power off mode function

If the LAT pin voltage is decreased to 0.55 V or lower, the power-off mode is entered. In this mode, the control by FB pin voltage is invalidated. If the VCC pin voltage decreases to 8.0 V or lower, switching is started, whereas if the voltage increases to 8.5 V or higher, switching is stopped. These operations are repeated to forma a lower-frequency burst waveform, thus achieving lower standby power. Since the output voltage becomes dependent on the turn ratio of the secondary winding of transformer to the VCC auxiliary winding, a DC-DC converter, etc. may become necessary.

#### (8) Frequency diffusion (Spread spectrum)

FA8AxxN perform frequency modulation of  $\pm$  7.0 kHz for switching frequency 65 kHz. This function enables more noise energy of the switching to disperse compared to the case with fixed frequency and obtains a conduction EMI reduction effect. While the reduction effect depends on the filter parts mounted on the power supply board, effective use of this function allows the reduction of the number of the filter parts and the constants.

In addition, Since the frequency diffusion function is always subjected to frequency variation, it is effective to reduce conduction EMI at light load.

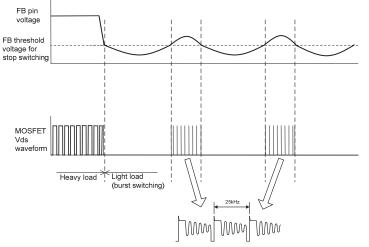

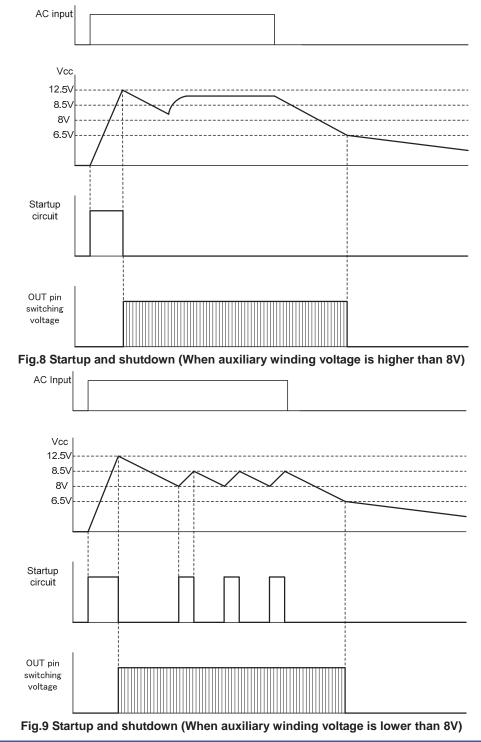

## (9) DSS(Dynamic Self Supply) function

When power is turned on, the capacitor connected to the VCC pin is charged by the current supplied to the VCC pin from the startup circuit via the HV pin, and voltage increases. When this voltage exceeds the ON threshold voltage of 12.5 V, the power supply for internal circuit is turned on, and switching is started. At this time, if the voltage supplied from the VCC auxiliary winding is higher than 8 V, the startup circuit is operated only at the time of startup, and after the startup, operation is performed with the voltage of the auxiliary winding used as the power supply. However, if the voltage supplied from the auxiliary winding decreases to lower than 8 V due to switching to low-output voltage in standby mode due to the time of latch stop by overvoltage and overload, operation is continued with the VCC voltage maintained between 8 V and 8.5 V by ON/OFF of the startup circuit.

With FA8A68N, only in the case of latch stop, this function interrupts operation, thus the VCC pin voltage decrease to the OFF threshold voltage, and automatic recovery is achieved by restarting the IC.

🔫 Fuji Electric Co., Ltd

## (10) Operation under overload (Automatic recovery type and timer latch type series are available.)

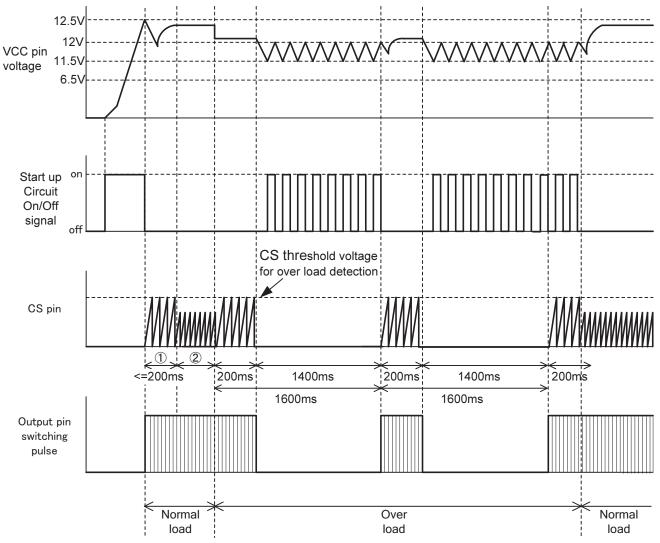

#### Automatic recovery type

If the CS pin voltage exceeds the overload protection CS threshold voltage, and that state continues for 200 ms, namely the overload protection stop delay time, under overload, switching is forcibly stopped.

When switching is stopped, supply of current from the auxiliary winding is stopped, and the VCC pin voltage decreases to 11.5 V or lower, the startup circuit is operated, and the VCC voltage is maintained within a range from 11.5 V to 12 V. When 1400 ms elapses after the switching is stopped, switching is resumed. If overload state is continuing at that time, start and stop operations are repeated. If normal load is resumed, operation goes back to normal.

Note, however, that since an up-down counter is used to count the overload protection stop delay time, to clear the up-count, down-count of the same period is required. Consequently, if a state where the overload period (1) is longer than the normal operation period (2) continues, count-up time is accumulated, and overload protection is actuated in time shorter than the overload protection stop delay time. Be careful if the operation undergoes overload and normal load conditions repeatedly.

At the time of startup, the output voltage must be increased to the setting within 200 ms.

The Automatic recovery function operates normally even when external power is input directly to the VCC pin because the automatic recovery operation is controlled by an integrated timer.

Fig.10 Operation under overload (Auto recovery type)

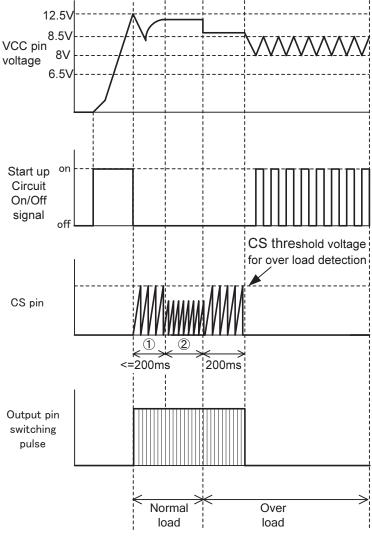

#### Timer latch type

If the CS pin voltage continues exceeding the overload protection CS threshold voltage for 200 ms, namely the overload protection stop delay time, or longer under overload, switching is stopped and the latch stop maintain this stopping state. In a state where switching is stopped by overload latch, VCC voltage is supplied by the startup circuit and operation suspension state is maintained.

Note, however, that since an up-down counter is used to count the overload protection stop delay time, to clear the up-count, down-count for the same period is required. Consequently, if a state where the overload period (1) is longer than the normal operation period (2) continues, count-up time is accumulated, and overload protection is actuated in time shorter than the overload protection stop delay time. Be careful if the operation undergoes overload and normal load conditions repeatedly.

To reset the overload latch, it is necessary to stop the supply of VCC voltage from the startup circuit by interrupting the input voltage, thereby decreasing the VCC voltage to 6.5 V, namely OFF threshold voltage, or lower.

Note that at the time of startup, the output voltage must be increased to the setting within 200 ms.

Fig.11 Operation under overload (Timer latch type)

#### (11) Over voltage protection

If the secondary output voltage reaches a state of overvoltage, the voltage of the auxiliary winding also increases. The VCC pin has a function of detecting the voltage of this auxiliary winding, and if the VCC pin voltage continues exceeding 25.5 V for 72  $\mu$ s, latch stop is implemented. If latch stop is implemented, the VCC pin voltage is maintained by the startup circuit, and the latch stop state is continued. This state is maintained until the VCC pin voltage decreases to the OFF threshold voltage at UVLO or lower by interrupting the input voltage.

With FA8A68N, the VCC pin voltage is not maintained by the startup circuit after the switching is stopped. Automatic recovery is implemented by restarting IC when the VCC pin voltage is decreased to the OFF threshold voltage.

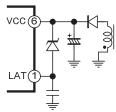

#### (12) Latch stop function by external signals

Latch stop is implemented by pulling up the LAT pin to 1.8 V or higher externally for 72  $\mu$ s or longer. After the latch stop, the VCC pin voltage is maintained by the startup circuit, and latch stop state is continued. This state is maintained until the VCC pin voltage decreases to the OFF threshold voltage at UVLO or lower by interrupting the input voltage.

With FA8A68N, the VCC pin voltage is not maintained by the startup circuit after the switching is stopped. Auto restoration is implemented by restarting the IC when the voltage is decreased to the OFF threshold voltage.

#### (13) Under voltage lockout function (UVLO)

To prevent circuit malfunction under under-voltage conditions, a low-voltage malfunction prevention circuit is integrated. If the VCC voltage increases from 0V, the IC starts operating when VCC = 12.5 V, and when the VCC voltage decreases, the operation is stopped when VCC = 6.5 V.

#### (14) Soft start function

When switching is started at the time of startup or automatic recovery after the interruption for overload protection, the overcurrent limit threshold voltage of the CS pin gradually increases, and furthermore the lowest ON width is fixed to Tmin2 (0.28  $\mu$ s) to prevent surge voltage Vds of the MOSFET at the time of startup. The overcurrent limit threshold voltage reaches approximately 470 mV when soft start time Tss of 11 ms has elapsed after the start of switching. Furthermore, when Tssend (17 ms) is reached, the lowest ON width switches to Tmin1 (0.56  $\mu$ s), and at the same time the frequency diffusion function is actuated.

Fig.12 Soft start function

# (15) Function of correcting the dependence of overload detection level on input voltage + correction amount adjusting function

The overload detection level varies depending on the input voltage. This IC detects the input voltage, and depending on that voltage, changes the overload protection CS threshold voltage, thereby correcting the dependency on the input voltage.

Since the dependency on the input voltage varies depending on the specifications of power supply, the correction amount can be adjusted using an external resistor mounted between the CS pin and the MOSFET.

# (16) Internal overheat protection function

If the IC temperature increases to 137°C or higher, switching is stopped by latch stop. Once latch stop is implemented, the VCC pin voltage is maintained by the startup circuit, and the latch stop state is continued. This state is maintained until the VCC voltage decreases to the OFF threshold voltage or lower by interrupting the input voltage.

With FA8A68N, the VCC pin voltage is not maintained by the startup circuit after the switching is stopped. Automatic recovery is implemented by restarting the IC when the voltage is decreased to the OFF threshold voltage.

# (17) Discharge function of the input filter X-capacitor at AC power interruption (Provided or not provided depending on series.)

By connecting the VH pin to the capacitor of the input filter by full-wave rectification connection, the X-capacitor of the input filter can be discharged when AC input power is interrupted. This function eliminates discharge resistance, thereby decreasing standby power.

The recommended capacitance of connectable X-capacitor is 2  $\mu\text{F}$  or lower.

(Requirement in UL60950 regarding electric shock: The voltage value of the power supply input part shall be attenuated to 37% or lower of the peak value within 1 s after the AC input voltage is interrupted.)

# 9. How to use each pin and advice for designing

(The values that appear in the following description are typical values, unless otherwise specified.)

#### (1) Pin No. 1 (LAT pin)

#### Function

( i ) Implements latch stop by external signals.

(ii) Adjusts operation mode switching point under light load.

(iii) Switches to power off mode

#### How to use

- ( i ) Latch stop by external signals

- Connection method

Pull up the LAT pin by external signals.

Figures 13 and 14 provide typical connections of the overvoltage protection circuit.

Operation

If the LAT pin voltage exceeds 1.8 V and this state continues for 72  $\mu$ s or longer, the output switching is stopped and thus latch stop is implemented.

If latch stop is implemented, the VCC pin voltage is maintained within a range from 8.0 V to 8.5 V by the startup circuit, and thus the latch stop state is continued. To reset that state, decrease the VCC voltage to 6.5 V, namely the OFF threshold voltage at UVLO, or lower.

With FA8A68N, the VCC pin voltage is not maintained by the startup circuit after the switching is stopped.

Automatic recovery is implemented by restarting the IC when the VCC voltage is decreased to the OFF threshold voltage.

(ii) Operation mode switching point adjustment under light load

(Adjustment of frequency decrease start points and burst operation start points)

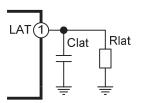

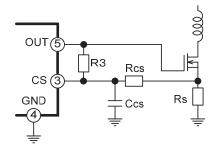

- Connection method Connect a resistor and a capacitor between the LAT pin

- and the GND. (See Fig. 15.)

- Operation

The frequency decrease start point can be adjusted in three stages depending on the capacitance of the capacitor.

At the time of startup, depending on the time until the 50  $\mu$ A source current output from the LAT pin charges the capacitor connected between the LAT pin and the GND to the specified threshold voltage, frequency decrease start FB voltage can be adjusted in three stages. See specifications for three frequency decrease start FB voltage conditions.

Depending on the resistance value, the burst operation start point can be adjusted linearly under light load.

During normal operation, 5  $\mu$ A source current is output from the LAT pin, and depending on the voltage generated at the resistor connected to the LAT pin and the GND, the pulse stop FB voltage of the FB pin can be adjusted linearly. The pulse stop FB voltage of the FB pin becomes approximately 0.63 times the voltage generated at the resistor connected between the LAT pin and the GND by the LAT pin source current of 5  $\mu$ A in normal operation.

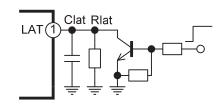

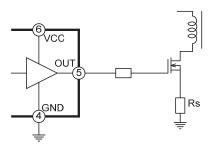

#### (iii) Power off mode switching function

Connection method

The LAT pin is pulled down by external signals.

Figure 16 is a typical connection diagram.

Operation

By decreasing the LAT pin voltage to 0.55 V, namely the power off mode threshold voltage, or lower, power off mode is entered.

Once the power off mode is entered, feedback control at normal FB pin voltage is stopped as shown in Fig. 17, switching start and stop are repeated based on the VCC pin voltage value, and by decreasing the burst frequency, lower standby power is achieved. If the VCC pin voltage increases to 8.5 V or higher, switching is stopped, whereas switching is started when the value decreases to 8.0 V or lower. Consequently, since the output voltage becomes dependent on the turn ratio of secondary winding of the transformer to the VCC auxiliary winding, a DC-DC converter, etc. may become necessary.

Fig.13 Overvoltage protection on the secondary side1

Fig.14 Overvoltage protection on the secondary side2

😑 🛛 Fuji Electric Co., Ltd.

FA8A60/61/70/71

Fig.15 LAT pin: Adjustment under light load

Fig.16 Power off mode switching circuit

Fig.17 Power off mode operation waveform

#### Advice for designing

(1) Caution in pulling up LAT pin by external signals

By increasing the LAT pin voltage to 2.0 V (max.) or higher for the period of 72  $\mu$ s, latch stop is implemented, but since the LAT pin voltage (absolute maximum ratings) is 3.3 V, the LAT pin must be clamped in order that the voltage falls within the range from 2.0 V to 3.3 V.

Therefore connect a Zener diode between the LAT pin and the GND as shown in Fig. 14.

Although the LAT pin integrates a Zener diode, the LAT pin current is 300  $\mu$ A or lower (absolute maximum ratings). The Zener diode connected between the LAT pin and the GND can also be omitted by suppressing the input current to 300  $\mu$ A or lower using a limiting resistor. Note, however, that delay time is generated due to external parts until the LAT pin voltage is increased because a resistor and a capacitor are connected between the LAT pin and the GND. Furthermore, attention should be paid because the IC integrates latch delay time of 72  $\mu$ s.

#### (2) Adjusting the frequency decrease start point

With this IC, the frequency decrease start point can be adjusted in three stages by the capacitor connected between the LAT pin and the GND. See the specifications for the three frequency decrease start FB voltage conditions.

To select each condition, connect the following capacitors between the LAT pin and the GND.

| frequency decrease     | Clat                                          |

|------------------------|-----------------------------------------------|

| start point            |                                               |

| To select high point   | 176pF= <clat=<264pf< td=""></clat=<264pf<>    |

| To select medium point | 800pF= <clat=<1200pf< td=""></clat=<1200pf<>  |

| To select low point    | 2640pF= <clat=<3960pf< td=""></clat=<3960pf<> |

Note that since the capacitor also has a role of stabilizing the threshold voltage at the burst operation switching point as described below, mount the capacitor at a point as close to the LAT pin as possible. Caution should be paid, in particular, when the capacitance of the capacitor is small.

#### (3) Adjusting the burst operation start point

With this IC, the burst operation start point can be adjusted linearly by the resistor connected between the LAT pin and the GND. The pulse stop FB voltage of the FB pin becomes approximately 0.63 times the voltage generated at the resistor connected between the LAT pin and the GND by the LAT pin source current of 5  $\mu$ A in normal operation.

Meanwhile, since external latch stop threshold voltage of 1.6 V (min.) and power off mode threshold voltage

(including hysteresis) of 0.65 V (max.) are set to the LAT pin voltage, the adjustable range of LAT pin voltage usable for burst switching point adjustment is from 0.65 V to 1.6 V.

Rlat>=LAT voltage(0.65V) / LAT pin source current(MIN) Rlat>=0.65V / 4.5uA

Rlat>=145kΩ(Recommended operation condition)

Rlat=<LAT voltage (1.6V) / LAT pin source current(MAX) Rlat=<1.6V / 5.5uA

Rlat=<290kΩ(Recommended operation condition)

Consequently, recommended resistance value must fall within the following range with fluctuation and temperature characteristics taken into consideration:

145 kΩ = <Rlat = <290 kΩ.

The pulse stop FB voltages are as follows when the following resistors are connected:

**270** k $\Omega$  (typ) (±1%): 270 k $\Omega$  (typ)\*5  $\mu$ A (typ)\*0.63=0.85 V **150** k $\Omega$  (typ) (±1%): 150 k $\Omega$  (typ)\*5  $\mu$ A (typ)\*0.63=0.47 V. (The pulse stop FB voltage is approximately 0.63 times the LAT pin voltage.)

Since the pulse stop FB voltage of the FB pin is approximately 0.63 times the LAT pin voltage in normal

operation, the pulse stop FB voltage fluctuates if noise enters the LAT pin. Therefore, connect the capacitor to be placed between the LAT pin and the GND at a position as close to the LAT pin as possible. Caution should be paid when the capacitance of the capacitor is small.

(4) Fluctuation of continuous switching frequency at the time of burst operation

The continuous switching frequency in burst operation is basically 25 kHz as shown in Fig. 17. However, if the overshoot voltage of the FB pin at continuous switching exceeds the FB threshold voltage at the minimum frequency, the frequency decrease range is entered, and as shown in Fig. 15, the frequency may fluctuate and audible noise may be generated from the transformer. In such a case, make an adjustment so as to decrease the burst operation start point and increase the frequency decrease start point, which may improve the situation.

| FB pin _                     |       | reshold voli<br>ium frequer | 0        |      |              |    |          |

|------------------------------|-------|-----------------------------|----------|------|--------------|----|----------|

| voltage <sup>-</sup><br>MOSF | CT    | ■ 25kHz                     | •        |      |              |    |          |

| Vds _<br>wavefo              |       |                             |          |      | $\mathbb{N}$ | MM | <u>۲</u> |

|                              | Fig.1 | 8 Burst op                  | peration | ı wa | vefor        | m  |          |

Fuji Electric Co., Ltd.

# (2) Pin No. 2 (FB pin)

#### Function

- ( i )Input feedback signals from the error amplifier on the secondary side.

- ( ii )Reduce switching frequency.

- (iii)Stops switching for burst operation.

#### How to use

(i) Feedback signal input

Connection method

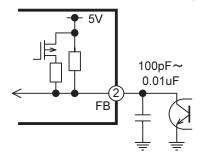

Connect the optocoupler corrector to this pin will allow reguration. At the same time, to prevent generation of noise, connect a capacitor in parallel to the optocoupler (Fig. 21).

Operation

Pin No. 2 is biased from the IC internal power supply via the resistance. The FB pin voltage is level-shifted and input into the current comparator to provide the threshold voltage of the MOSFET current signals to be detected with the CS pin.

#### (ii) Frequency decrease function

Connection method

The same as feedback signal input in ( i )

Operation

The switching frequency in normal operation mode is set to 65 kHz inside the IC. If the FB pin voltage decreases under light load, the frequency decreases almost linearly in proportion to this voltage. The lowest frequency is 25 kHz.

The frequency decrease start point can be adjusted in three stages depending on the capacitance of the capacitor connected between the LAT pin and the GND as shown in Fig. 22.

#### (iii) Burst operation

- Connection method

- The same as feedback signal input in ( i )

- Operation

FB pin voltage decreases under light load. If the FB pin voltage decreases to lower than the pulse stop FB voltage, switching is stopped. On the contrary, if the FB voltage increases to higher than the pulse stop FB voltage, switching is restarted. By repeating this operation, burst operation is achieved. To undershoot the FB pin voltage significantly at the time of burst operation, the internal FB pin resistance is switched (Fig. 21).

With this IC, the pulse stop FB voltage, which serves as a burst operation switching point, can be adjusted linearly in accordance with the resistance value of the resistor connected between the LAT pin and the GND as shown in Fig.20 .

Fig.19 FB pin voltage and oscillating frequency

load

#### Advice for designing

The FB pin provides threshold voltage of the current comparator. If noise is added to the pin, output pulse fluctuation may result. To prevent generation of noise, a capacitor having the capacitance of approximately 100 pF to 0.01  $\mu$ F is connected for use as shown in Fig. 21.

Fig.21 FB pin circuit

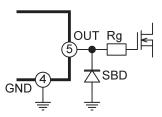

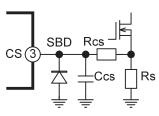

# (3) Pin No. 3 (CS pin)

#### Function

( i ) Detects the current value of MOSFET and limits the current.

(ii) Detects overload state.

(iii) Adjusts the correction amount of dependency of the overload detection level on the input voltage.

#### How to use\_

( i ) Current detection and current limiting

Connection method

Connect a current detecting resistor Rs between the MOSFET source pin and the GND. The current signals of the MOSFET generated in the resistor are input (Fig. 22).

Operation

The current signals of the MOSFET input to the CS pin is then input to the current comparator, and if it reaches the threshold voltage determined by the FB pin, the MOSFET is turned off. This FB pin voltage fluctuates due to the feedback circuit from the output voltage to control the MOSFET current.

The CS pin voltage also is input in the OLP\_CS comparator, and the MOSFET current under overload, etc. is limited to the current determined by the overload CS threshold voltage and the current detection resistor Rs.

(ii) Overload detection

Connection method

The same as the current detection and current limiting in ( i )

Operation

If the state where current is limited because the CS pin voltage has reached the overload CS threshold voltage continues for 200 ms or longer, that state is judged to be overload state. In the case of timer latch type, switching is stopped, detecting overload state, and the latch stop mode maintain this stopping state. In the case of automatic recovery type, intermittent operation is performed under overload, and normal operation is resumed when overload state is reset. See 8.(9) Overload operation for details.

(iii) Adjusting the correction amount of dependency of overload detection level on the input voltage

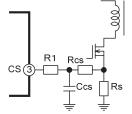

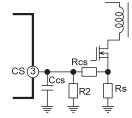

#### Connection method

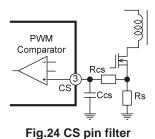

As shown in Fig. 23, add a resistor Rcs between the current detecting resistor of the MOSFET and the CS pin. If the CS pin includes a CR filter, adjustment can be made using that resistance value. (Fig. 24)

Operation

Fuji Electric Co., Ltd.

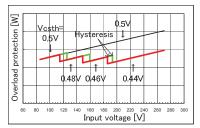

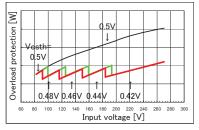

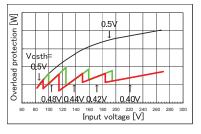

The overload detection level becomes high as the input voltage becomes high. This IC detects the input voltage,

and corrects the dependency of the overload detection level on the input voltage by switching the overload protection CS threshold voltage (Vcsth) of the CS pin at each point of the input voltage. However, since the dependency of overload detection level on the input voltage varies depending on the specifications of the power supply (such as L value of the transformer and output capacity etc.), the correction amount can be adjusted.

As the adjusting method, at the time of startup only, constant source current (100  $\mu$ A) is output from the CS pin for a specified period of time, and the correction amount is adjusted depending on the voltage generated at the resistor connected between the CS pin and the GND (such as a resistor inserted between the current detecting resistor of the MOSFET and the CS pin). The correction amount can be adjusted under three conditions. See Figs. 22, 23, and 24 for the notion of three correction conditions. Weak has the smallest amount of input voltage correction, followed by Middle, and then by Strong.

In addition, since hysteresis applies to the overload protection threshold voltage switching point and overload detection level varies in accordance with the increase/decrease of the input voltage, adjustment requires special attention.

Fig.22 CS pin current detection

Fig.23 Adjustment of the correction amount of overload on input voltage (1)

#### Advice for designing

#### (1) Inserting a filter

This IC integrates a blanking function to suppress the effect of surge current that is generated at turn-on part of the MOSFET. However, if the surge generated at this turn-on part is large, or due to external noise, malfunction may result. In such cases, add a CR filter to the CS pin as shown in Fig. 24.

Select a filter depending on the magnitude of the noise, but the selection requires special attention because delay factor increases, thereby increasing fluctuation in overload detection level if the time constant of Rcs × Ccs increases. Install the capacitor Ccs at a place as close to the IC as possible to ensure effective operation, and pay special attention in installing wiring. Depending on the time constant of the filter, the overload detection level and load point for switching into burst operation (burst point) vary, thus causing generation of audible noise and affecting standby power. Be sure to check thoroughly.

(2) Adjusting the correction amount of dependency of overload detection level on the input voltage